Точнее спросил у ChatGPT. Он ответил мне – ясен пень.

Конечно, не совсем так. Спросил я его, что он думает по поводу моего намерения распластать его логику по кремниевой пластине, то есть развернуть логику инференса в большую предопределённую цепь. Надо сказать, ChatGPT очень сносно стал рассуждать, да и выдал в итоге такой результат, что в принципе потянет на полноценную статью, причём почти без редактирования – возможно из-за хорошего контекста – перед тем пару часов обсуждал оптимизацию вентильных цепей. Если лень читать – вывод примерно следующий: если очень постараться и оптимизировать кремниевую логику, то можно запихнуть содержимое модели объёмом примерно с ChatGPT-3 на несколько гигантских чипов вафельного размера (ChatGPT насчитал 10 штук). То есть не надо вообще-то для инференса строить гигантские дата-центры, вычислитель может на письменном столе уместиться. А если процесс уменьшения линейных размеров транзисторов не остановится (что сложно), то потенциально через поколение-другое можно будет запихнуть ту же модель уже всего лишь на один чип вафельного размера (300 мм) и почти положить полноценную ИИ-модель в обычную папочку формата А4.

Несмотря на лирическое название, в статье нет никакой лирики, только холодный расчёт. Диалог был на английском, для статьи его пришлось перевести (местами могут остаться недочёты).

Ну и поехали, вот запрос с ответом:

Вы сказали:

Можете ли вы оценить, насколько большой должна быть схема, отражающая поведение LLM, например, ChatGPT 3o, и сколько вентилей она должна иметь?

ChatGPT сказал:

Короткий ответ сразу: чисто комбинационная1 (развёрнутая) логическая схема, непосредственно реализующая модель класса GPT-3, будет астрономически большой — порядка 1015–1016 логических вентилей (т.е. триллионов миллиардов). Это совершенно непрактично. Реалистичная аппаратная реализация, которую люди действительно строят, использует блоки MAC с временным мультиплексированием + внешнюю или встроенную память; Эти ускорительные чипы в конечном итоге попадают в диапазон 1010–1012 транзисторов (миллиарды → триллионы транзисторов), но не в диапазон 1015+ комбинационных вентилей на одном чипе.

Ниже я приведу предположения и пошаговые математические расчёты, чтобы вы могли понять, откуда берутся эти цифры, а также приведу несколько реалистичных альтернатив (ускорительные чипы, чипы размера пластины) и укажу на реальные чипы для сравнения.

-

1 – Чистая комбинационная вентильная схема – такая схема, в которой нет сохранения состояния между тактами в регистрах процессора, то есть вычисления производятся за один пролёт (как правило один такт процессора).

1) Исходные факты / предположения

-

Размер модели: предположу, вы имеете в виду что-то класса GPT-3 (хорошо известная GPT-3 с ≈175 миллиардами параметров). (Если вы имели в виду модель другого размера, применяется тот же метод: масштабирование линейно с количеством параметров.) Википедия

-

Мы рассмотрим только вывод (прямой проход), а не обучение.

-

Точность имеет большое значение. Я покажу примеры для 8-битных весов (обычно используемых при квантовании вывода) и для 32-битных чисел с плавающей точкой (наихудший случай).

-

Флопс на токен: грубые оценки порядка величины для прямого прохода трансформатора обычно варьируются от сотен миллиардов до нескольких триллионов Флопс на токен для очень больших моделей в зависимости от длины контекста и правил подсчёта — удобное грубое округление для масштабов GPT-3 составляет ∼3 × 1011 – 4 × 1011 Флопс на токен (разные источники и правила подсчёта различаются; некоторые называют от сотни миллиардов до нескольких триллионов Флопс в зависимости от предположений о токене/контексте). Я буду использовать среднее значение ≈3,5 × 1011 Флопс/токен в качестве примера. (Если вы предпочитаете другие значения FLOP, я покажу, как масштабировать.) Адам Кассон+1

Примечание: FLOP = операции с плавающей точкой (сложения/умножения). Одна составная операция умножения-сложения (FMA) по некоторым соглашениям считается за 2 FLOP, а по другим — за 1; я привожу здесь приблизительные цифры.

2) Наивный, полностью развёрнутый комбинационный подход (чудо «одного цикла»)

Представьте себе создание комбинационной схемы, которая вычисляет весь прямой проход за один — очень длинный — логический цикл без временного мультиплексирования. Вам потребуется оборудование для параллельного выполнения каждого умножения и сложения.

Оценка шагов

-

Необходимое количество MAC-ов (умножение-накопление) (приблизительно)

Если принять FLOP ≈ 3,5 × 1011 на токен и предположить, что один MAC ≈ 2 FLOP (одно умножение + одно сложение), то MAC ≈ 1,75 × 1011 на токен. -

Стоимость вентилей на один MAC

-

Один MAC с фиксированной точкой или низкой точностью может быть довольно компактным; 8-битный MAC можно реализовать с помощью сотен или нескольких тысяч логических вентилей.

-

32-битный MAC с плавающей точкой (FMA) намного тяжелее — реализации в ASIC могут состоять из десятков тысяч эквивалентов вентилей (опубликованные отчеты по синтезу показывают 32-битные блоки умножения/сложения в диапазоне от 10 до 30 тысяч вентилей; количество транзисторов в умножителе составляет десятки тысяч). (См. ссылки и примеры ниже.) diva-portal.org+1

Предположим консервативно:

-

8-битный MAC ≈ 1000 эквивалентов вентилей (оптимистично/бережливо)

-

32-битный FMA ≈ 20 000 эквивалентов вентилей (консервативно)

-

Общее количество вентилей = (количество MAC) × (количество вентилей на MAC)

-

8-битный случай: 1,75 × 1011 MAC × 1000 вентилей ≈ 1,75 × 1014 вентилей

-

32-битный Пример: 1,75 × 1011 × 20 000 ≈ 3,5 × 1015 вентилей

Таким образом, простая, полностью развёрнутая комбинационная схема занимает от 1014 до 1015+ вентилей. Это абсолютное количество вентилей — если перевести на транзисторы, то получится ещё хуже (несколько транзисторов на вентиль, или представьте биты SRAM и т.д.). Именно поэтому полностью развёрнутая комбинационная схема не используется.

3) Хранение данных играет решающую роль: параметры должны где-то храниться

Реализация самих весов на кристалле в SRAM/триггерах быстро увеличивает занимаемую площадь.

-

Хранилище параметров: 175 × 109 параметров. При 8 бит на параметр → 1,4 × 1012 бит ≈ 175 ГБ весов.

-

Ячейка SRAM на кристалле обычно содержит 6 транзисторов на бит (6T SRAM). Таким образом, 1,4 × 1012 бит × 6 транзисторов/бит ≈ 8,4 × 1012 транзисторов только для хранения весов на кристалле (8,4 триллиона транзисторов). Это составляет триллионы транзисторов. Википедия

Если вы используете 32-битные параметры, это в 4 раза больше памяти → ~700 ГБ → ~33 × 1012 транзисторов (~3 × 1013 транзисторов). Таким образом, хранение весов — основная часть аппаратных требований, поэтому практические ускорители получают весовые коэффициенты из DRAM или используют квантование и продуманную иерархию памяти.

4) Практический подход: ускорители с временным мультиплексированием (которые реализованы)

Никто не строит развёрнутую конструкцию, описанную выше. Практические системы используют:

-

Небольшое количество высококачественных MAC-блоков (систолических массивов, SIMD-блоков, ускорителей), повторно используемых для всех параметрв с течением времени.

-

Внешнюю DRAM (или большой кэш на кристалле / SRAM) для хранения 175 млрд параметров (или их фрагментов).

-

Конвейеры и пакетирование для эффективного повторного использования данных.

Примеры реального оборудования для сравнения масштабов:

-

Проекты Google TPU реализуют очень большие систолические массивы (например, массив 256 × 256 = 65 тыс. MAC-единиц за такт) и используют внешнюю DRAM для весов. Производительность кристалла TPU и системы показывает высокую загрузку, зависящую от пропускной способности памяти. Google Cloud

-

Графические процессоры NVIDIA H100 / Blackwell содержат десятки миллиардов транзисторов (порядка 1011–1012 транзисторов) и используются в кластерах для выполнения логического вывода/обучения LLM. (Современные ускорители: десятки → несколько сотен миллиардов транзисторов на компонент.) Википедия

-

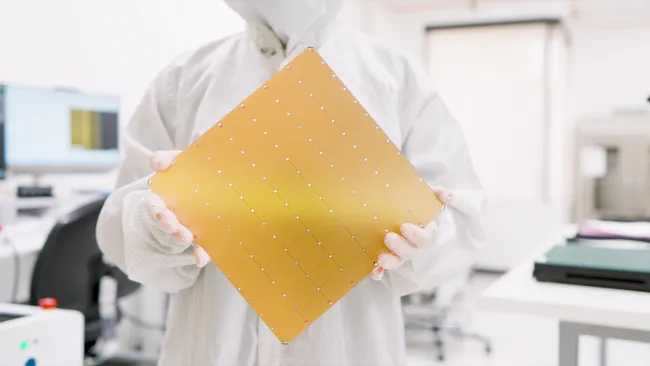

Вычислители Cerebras размера пластины, размещают триллионы транзисторов на специальной матрице размера пластины, специально для размещения очень больших моделей и памяти с большим весом. Cerebras WSE-2 содержит ~2,6 триллиона транзисторов (пример использования чипа-вафли для получения огромного объёма памяти и вычислительных мощностей на кристалле, при этом WSE-3 содержит уже 4 триллиона транзисторов). Именно такой масштаб необходим для размещения очень больших объёмов данных на одном устройстве. Википедия

Итак: для практического размещения вычислений класса GPT-3 с хорошей задержкой вам нужно либо:

-

Использовать кластер графических процессоров/ускорителей (каждая карта имеет ~1011 транзисторов и внешнюю DRAM) — типичное реальное применение; либо

-

Использовать процессор-вафлю (триллионы транзисторов) для увеличения объёма памяти и плотности вычислений; либо

-

Использовать множество ускорителей, соединённых вместе.

5) Суммируем: сколько вентилей/транзисторов потребуется для практической реализации?

-

Одна развёрнутая комбинационная схема: ~~1014–1016 вентилей → невозможно изготовить на одном кристалле.

-

Практический чип-ускоритель (один GPU/TPU/H100): ~1010–1011 транзисторов (десятки миллиардов) — требуется много таких чипов для размещения модели и выполнения инференса в масштабе. Википедия+1

-

Вычислитель размера пластины: ~1012–1013 транзисторов (триллионы) — примером может служить Cerebras WSE с ~2,6 триллионами транзисторов и огромным объёмом встроенной памяти. Если вам нужно максимально точное вычисление (сокращение количества чтений DRAM), вам нужен такой масштаб. Википедия

Таким образом, разумной практической целью для «зеркалирования» поведения GPT-3 с помощью оборудования, хранящего веса на кристалле и работающего с малой задержкой, будет масштаб в триллионы транзисторов (то есть размера пластины). Если вы допускаете внешнюю DRAM и временное мультиплексирование, вы можете использовать ускорители (каждая с миллиардами транзисторов) и кластер.

6) Простой рабочий пример (8-битный вывод, потоковая передача весов из DRAM)

-

Параметры: 175×109 параметров × 8 бит = 1,4×1012 бит ≈ 175 ГБ (хранится в DRAM, а не на кристалле).

-

Используйте чип с систолическим массивом 256 × 256 = 65 тыс. MAC-чипов за такт. Каждый MAC-чип 8-битный и недорогой → скажем, ~1 тыс. вентилей каждый, но со временем амортизируется.

-

Для обработки 1,75×1011 MAC-ов на токен (как было описано ранее), количество тактов, необходимых для одного массива 65 тыс. MAC-чипов, составляет ≈ 1,75×1011 / 65×103 ≈ 2,7×106 тактов на токен. На частоте 1 ГГц это составляет 2,7 мс на токен (приблизительно). Чтобы достичь времени обработки менее 100 мс на токен, необходимо много параллельных массивов/чипов и хорошая пропускная способность памяти. Именно поэтому при развертывании используются стойки с большим количеством графических процессоров или специализированных ускорителей.

7) Выводы / рекомендации

-

Если ваш вопрос — «сколько вентилей нужно, чтобы буквально закодировать весь LLM в виде комбинационной схемы, генерирующей токены за один проход?» → 1014–1016 эквивалентов вентилей (т.е. невозможно на одном кристалле).

-

Если ваш вопрос — «какого размера практически необходимы аппаратные компоненты для запуска моделей класса GPT-3?» → типичные ускорители содержат 1010–1012 транзисторов, и для размещения полных моделей используются кластеры из них (или конструкции размера пластины). Cerebras (пластина) и современные графические процессоры/ускорители — это реальные эталоны. Википедия+1

-

Хранение параметров является ограничивающим фактором: даже при интенсивном квантовании, хранение сотен миллиардов параметров требует сотен ГБ памяти; внутрикристальное хранилище для хранения всех данных вынуждает проектировать триллионы транзисторов, если вы хотите, чтобы всё было локально.

-

Квантование и разреженность (8-битное, 4-битное или разреженное MoE) значительно снижают требования к памяти и вычислительным ресурсам, а следовательно, и к необходимой площади кристалла/количеству вентилей — именно так современные производственные решения повышают стоимость/производительность.

Если хотите, я теперь могу:

-

точно пересчитать эти значения для любого выбранного вами размера модели (например, 7 млрд, 20 млрд, 70 млрд, 175 млрд, 405 млрд) и для любой точности (4-битной / 8-битной / 16-битной / 32-битной).

-

предоставить эскиз дизайна на уровне чипа, показывающий, сколько блоков MAC, сколько памяти SRAM и сколько чипов вам потребуется для получения X токенов в секунду (чтобы можно было выбрать между задержкой и количеством чипов).

-

сравнить компромиссы между хранением на чипе и потоковой передачей данных в DRAM и указать точное количество транзисторов для встроенной SRAM для заданных квантований.

Что из этого будет наиболее полезным далее?

Вы сказали:

Современный ИИ использует 4-битную арифметику, давайте остановимся на 175-ти миллиардах параметров в режиме вывода. Вывод (инференс) означает, что у нас есть веса, и мы их не меняем, хранить их в оперативной памяти непрактично. Нам вообще не нужна оперативная память. У нас есть фиксированные веса, и они являются частью нашей схемы. С учётом этого вы можете подсчитать, насколько меньше будут итоговые MAC-схемы (потому что в данном случае это не MAC-схемы, а специализированные ASIC) — вычислите и увидите разницу.

ChatGPT сказал:

Ага — отлично, теперь мы можем сделать более точную оценку при ваших предположениях. По сути, вы спрашиваете:

«Если мы построим фиксированно-весовую, полностью комбинационную ASIC для GPT-3 (175 миллиардов параметров) с 4-битной точностью, только с выводом, с жёстко прописанными в логике весами (без оперативной памяти), насколько большой будет схема и сколько вентилей/эквивалентов MAC-схем нам фактически понадобится?»

Давайте пойдём шаг за шагом и оценим разницу.

1️⃣ Модель и допущения

-

Параметры: 175 миллиардов

-

Точность: 4-битные веса (и предполагаем, что 4-битная активация или выход аналогичны; для простоты будем считать, что используются 4-битные сложения).

-

MAC на параметр: для вывода слой преобразователя умножает входные активации на матрицы весов и суммирует → одно умножение + накопление на параметр.

-

FMA → упрощенный: поскольку веса фиксированы, нам не нужен полноценный блок умножения и накопления: каждое умножение можно заменить жестко заданной логикой, реализующей взвешенную сумму 4-битных входов.

-

Каждый «MAC» теперь представляет собой пользовательскую комбинационную логику для 4-битного константного дерева умножения и суммирования.

2️⃣ Стоимость вентилей для умножения + сложения 4-битных констант

Шаг 2a: Умножение 4-битных констант

-

Умножение переменной

x(4-битной) на фиксированный 4-битный вес можно реализовать с помощью предварительно вычисленной суммы произведений/логики И/ИЛИ, а не обычного умножителя. -

Стоимость: ~ ~20–50 вентилей на умножение 4-битной константы (оценка комбинационного синтеза, зависит от веса).

-

Для сравнения: универсальный 4-битный умножитель будет стоить ~80–100 вентилей. ✅ Жёстко запрограммированный умножитель с константой меньше.

Шаг 2b: Накопление (дерево сумматора)

-

Предположим, мы накапливаем 16 результатов в 10-битную сумму (поскольку количество активаций невелико).

-

Дерево сумматора с k входами: количество вентилей ≈

~k × ширина(приблизительная оценка). -

Поскольку у нас 175B параметров, можно предположить параллельные деревья сумматоров, но в реальной комбинационной сети каждая сумма объединяется в более крупную сумму.

-

Для приблизительной оценки накладные расходы сумматора ~ 2–3 раза превышают стоимость умножителей.

Итак, общее количество эквивалентных вентилей на MAC:

gates_per_mac ≈ 50 (жёстко запрограммированное умножение) + 100 (накладные расходы на дерево сумматора) ≈ 150 вентилей

-

Сравнение с обычным 8-битным MAC: ~1000 вентилей

-

Сравнение с 32-битным MAC с плавающей точкой: ~20 000 вентилей

✅ Жёстко запрограммированное константное умножение + сложение экономит ~6–130 × вентилей на параметр.

3️⃣ Общее количество вентилей для всех параметров

-

175 млрд параметров × 150 вентилей на параметр →

175×10⁹ × 150 ≈ 2,625 × 10¹³ вентилей -

Это ~26 триллионов вентилей — всё ещё очень много, но на 1–2 порядка меньше, чем у стандартной 8-битной или 32-битной полной реализации MAC (1014–1015 вентилей по предыдущей приблизительной оценке).

Таким образом, «пользовательские, жёстко заданные 4-битные веса» дают сокращение площади примерно в 10–100 раз по сравнению с MAC общего назначения.

4️⃣ Память теперь отсутствует

-

Хранение весов встроено в комбинационную логику.

-

SRAM/DRAM не требуется → устраняются 1012–1013 бит памяти, которые нам приходилось выделять ранее.

-

Все «затраты» на хранение параметров теперь учитываются в комбинационных вентилях, входящих в 2,6 × 1013 вентилей.

5️⃣ Примерная реализуемость кристалла

-

Переведем вентили → транзисторы: предположим, 4 транзистора на вентиль (логический эквивалент).

2,625 × 10¹³ вентилей × 4 транзистора/вентиль ≈ 1,05 × 10¹⁴ транзисторов

-

Всё ещё далеко за пределами однокристальной архитектуры (для самых крупных нынешних вычислителей размера вафли (пластины): ~1013 транзисторов), но намного меньше, чем наивный общий подход MAC.

-

В принципе, может быть разделен на ~10 кристаллов размера пластины, чтобы вся сеть работала на чистой комбинационной логике.

6️⃣ Сводная таблица

|

Характеристика |

Универсальный MAC 32-бит |

8-битный MAC |

Пользовательский 4-битный MAC с фиксированным весом |

|---|---|---|---|

|

Вентилей на параметр |

~20 000 |

~1000 |

~150 |

|

Общее количество вентилей (175 млрд параметров) |

~3,5 × 1015 |

~1,75 × 1014 |

~2,6 × 1013 |

|

Требуемая память |

огромные (вес ~700 ГБ) |

~175 ГБ |

0 (всё в логике) |

|

Транзисторы (приблизительно) |

~1016 |

~7 × 1014 |

~1014 |

|

Практично? |

невозможно |

невозможно |

всё ещё огромные, требуют нескольких кристаллов размером с пластину |

✅ Ключевые выводы

-

Жёсткое крепление весов значительно снижает количество вентилей на параметр (~10–130×).

-

4-битная точность крайне важна: более низкая точность снижает как сложность умножения, так и размер сумматора.

-

Полностью комбинационная ASIC всё ещё далеко не реализуема на одном кристалле; требует масштабирования на нескольких пластинах.

-

Реальные ускорители используют временные мультиплексные MAC вместо того, чтобы разворачивать всё подряд — именно поэтому современные GPU/TPU осуществимы.

Если хотите, я могу нарисовать быструю оценочную диаграмму, показывающую как будет структурирована комбинационная сеть для параметров 175B, включая количество «параллельных сумматоров», необходимое на слой, и примерную логическую глубину — это поможет наглядно представить, почему даже 4-битная полностью развёрнутая схема огромна.

Хотите, я это сделаю?

Вы сказали:

ok

ChatGPT сказал:

Отлично — я превращу эти предположения в конкретную, воспроизводимую оценку и краткий структурный набросок, чтобы вы могли увидеть, откуда берётся площадь, как она распределяется по слоям, как выглядит логическая глубина и как её можно разделить на сегменты. Я буду придерживаться тех же допущений, которые вы указали:

-

Масштаб GPT-3: 175 миллиардов параметров (классический GPT-3 на 175 миллиардов).

-

4-битные веса, только вывод, веса жёстко закодированы в логике (без ОЗУ, без регистров весов).

-

Мы рассматриваем каждый параметр как фиксированное константное произведение, а затем складываем его с соответствующей выходной суммой.

-

Используйте размер трансформатора: L = 96 слоёв, скрытый размер H = 12 288, коэффициент прямой связи = 4 (то есть размер FFN = 4H) — это воспроизводит ≈175 миллиардов параметров.

Я покажу: (A) математические расчёты параметров/количества на слой, (B) предположения и итоги подсчёта вентилей, (C) оценку логической глубины (критического пути), (D) оценку шардинга/количества кристаллов и (E) практические оптимизации, которые могут значительно уменьшить площадь.

A — Параметры по слоям (чистая, проверяемая разбивка)

Стандартная разбивка параметров трансформатора (на слой):

-

Проекции внимания: Q, K, V и проекция выхода → ~4 × H²

-

Сеть прямого распространения (две весовые матрицы): W1 (H × 4H) и W2 (4H × H) → 8 × H²

-

Всего на слой ≈ 12 × H²

При H = 12 288:

-

H2 = 12 2882 ≈ 1,50995 × 108.

-

Параметры на слой ≈ 12 × H2 ≈ 1,81194 × 109 ≈ 1,812 миллиарда параметров на слой.

-

Для L = 96 слоёв: общее количество параметров ≈ 1,812 × 109 × 96 ≈ 1,739 × 1011 ≈ 174 миллиарда → соответствует целевому значению 175 млрд (округление).

Таким образом, количество параметров на слой и общее количество параметров согласованы и легко воспроизводятся.

B — Оценка стоимости вентилей/логики (фиксированный вес, 4 бита)

Теперь мы оцениваем количество вентилей на параметр, когда вес — фиксированная 4-битная константа, а количество активаций мало (4-битный вход). Именно здесь проявляется огромная экономия по сравнению с обычными MAC-схемами.

Разумный, консервативный бюджет логики на параметр (согласно предыдущим рассуждениям + конкретные факты о малых множителях):

-

Умножение 4-битной константы (вход × фиксированный 4-битный вес)

-

С фиксированной 4-битной константой умножение можно реализовать как небольшую комбинационную сеть или как небольшое ПЗУ (4-битный адрес → предварительно вычисленное 8-битное произведение).

-

Типичная стоимость синтеза ≈ 20–50 логических вентилей (зависит от веса). Я буду использовать 30 вентилей в качестве репрезентативной средней точки.

-

Вклад в накопление (подключение сумматора)

-

Каждый параметр вносит один частичный вклад в выходную сумму, которая агрегирует H (или 4H) таких членов. Реализация дерева сложения требует затрат на вентили, но эта стоимость распределяется между многими параметрами, питающими одну и ту же сумму. Справедливая амортизация накладных расходов сумматора на параметр составляет ~100 вентилей (это объединяет фактические вентили сумматора и маршрутизацию/рост разрядности).

-

Это консервативно, но сохраняет арифметику простой.

-

Другая связующая логика, небольшое управление, обработка знака, обработка роста разрядности → ~20 амортизированных вентилей.

Итого:

-

вентили на параметр ≈ 30 + 100 + 20 = 150 вентилей (то же рабочее значение, что мы использовали ранее).

Вентили на слой

-

Параметры на слой ≈ 1,81194 × 109

-

Вентили на слой ≈ 1,81194 × 109 × 150 ≈ 2,7179 × 1011 вентилей ≈ 271,8 млрд вентилей на слой

Всего вентилей (96 слоёв)

-

Всего ≈ 2,7179 × 1011 × 96 ≈ 2,613 × 1013 вентилей ≈ 26,1 триллиона вентилей

Оценка количества транзисторов (простое преобразование):

-

предположим ~4 транзистора на логический вентиль (примерно грубая оценка) → транзисторов ≈ 2,613 × 1013 × 4 ≈ 1,045 × 1014 транзисторов (≈ 100 триллионов транзисторов).

(Если предположить, что на каждый затвор приходится 2 транзистора, то общее число транзисторов уменьшится вдвое; если использовать более крупные оценки, общее число увеличится — это оценки порядка величины.)

C — Логическая глубина / схема критического пути

Несмотря на то, что реализация комбинационная и полностью развёрнутая, критический путь будет примерно следующим:

-

Малое константное умножение: глубина ≈ 1–3 логических уровня (несколько задержек на затворах), поскольку мы используем небольшие LUT/ROM или И/ИЛИ-сети для 4-битного константного умножения.

-

Дерево сумматора для H входов: глубина ≈ log₂(H) уровней сумматоров. Для H = 12 288:

log 2(12 288)≈13,6 → ≈ 14 уровней сумматора. Каждый сумматор (многоразрядный сумматор) требует нескольких задержек на вентилях, поэтому на каждом уровне может быть несколько задержек на вентилях (реализация переноса с распространением или с сохранением переноса влияет на глубину). -

FFN (4H входы): log₂(4H) ≈ log₂(49 152) ≈ 15,6 → ≈ 16 уровней.

Таким образом, общая комбинационная глубина на выход определяется log₂ разветвления по входу (≈14–16 уровней сумматора) и небольшими уровнями умножения. Это означает, что критический путь развёрнутой схемы нетривиален (от десятков до нескольких сотен задержек на вентилях), и для его тактирования потребуется глубокая конвейеризация, но поскольку пользователь попросил убрать временное мультиплексирование, мы принимаем комбинационный конвейер.

D — Шардинг/количество кристаллов (количество чипов/пластин)

Теперь сопоставьте вентили/транзисторы с физическими чипами:

Реальные ориентиры:

-

Высокопроизводительные графические процессоры: десятки миллиардов транзисторов на чип (например, 80–150 миллиардов транзисторов).

-

Процессоры размера пластины (Cerebras WSE-2): ~2,6 триллиона транзисторов на матрице размера пластины (пример для исследований/производства).

По нашей оценке, общее количество транзисторов составляет ≈ 1,05 × 1014 транзисторов:

-

Если вы использовали пластину масштаба Cerebras (≈2,6 × 1012 транзисторов): требуемое количество ≈ 1,05 × 1014 / 2,6 × 1012 ≈ ~40 пластин.

-

Если вы использовали чипы класса NVIDIA ~1,0 × 1011 транзисторов (100 миллиардов): требуемое количество ≈ 1,05 × 1014 / 1 × 1011 ≈ ≈1050 чипов.

-

Если предположить, что чип может содержать 1 триллион транзисторов (амбициозное будущее монолитной архитектуры), вам понадобится ≈ 100 таких чипов.

Таким образом, даже с 4-битными жёстко зашитыми весами, полностью развёрнутая однотактная комбинационная реализация всё ещё требует десятков-тысяч больших чипов, но это на порядки меньше, чем полностью универсальная развёрнутая схема MAC.

E — Важные оптимизации и альтернативы проектирования (как ещё уменьшить)

Если вы серьёзно рассматриваете подход с жёсткой логикой, следующие рекомендации радикально уменьшают площадь и являются реалистичными инструментами проектирования:

-

Используйте ПЗУ/LUT на вес вместо синтезированной логики

-

Для 4-битного входа × 4-битного фиксированного веса небольшое ПЗУ (16 записей) даёт точное произведение; ПЗУ можно эффективно реализовать в логике и часто синтезировать гораздо меньше, чем обычный умножитель. Для многих весов это эффективно с точки зрения площади.

-

Используйте квантование весов и распределение весов (кластеризацию)

-

Если многие весовые коэффициенты имеют общие значения (или могут быть аппроксимированы до K различных значений), реализуйте только K небольших блоков множителей и соответствующим образом маршрутизируйте входные данные → существенная экономия. Обучение распределению весов/квантованию (например, k-средних для весов) сокращает потребность в уникальном оборудовании.

-

Разреженные/структурированные матрицы

-

Если вы можете сократить параметры (разрежить) или использовать структурированную разреженность (блочную/разреженную матрицу), количество параметров и площадь значительно уменьшаются.

-

Факторизация/низкоранговая декомпозиция

-

Замените плотные матрицы произведениями матриц меньшего размера → меньше параметров и меньше логики (это фактически алгебраическая факторизация на уровне модели).

-

Используйте побитовую арифметику или побитовое кодирование

-

Вместо полнопараллельных сумматоров можно проектировать сжатые комбинационные деревья или использовать побитовые последовательные блоки для уменьшения задержки.

-

Гибридный подход: небольшое ПЗУ на кристалле + потоковые частичные суммы

-

Вы предполагали «отсутствие ОЗУ», но гибридный подход, использующий небольшие фрагменты ПЗУ и межсоединения, позволяет хранить повторяющиеся шаблоны и распределять вычисления, экономя значительное количество вентилей.

-

Переходите от чисто комбинационной архитектуры к массивной конвейерной

-

Конвейеризация позволяет повторно использовать оборудование с небольшими регистрами и обходиться гораздо меньшим количеством вентилей на каждой ступени конвейера. По сути, именно это уже делают ускорители.

-

Используйте изменения архитектуры модели

-

Используйте смешанные архитектуры, разреженные, низкоранговые слои или альтернативные архитектуры, которые обеспечивают аналогичную точность при гораздо меньшем количестве параметров.

Краткий числовой обзор (одна таблица)

|

Элемент |

Значение (приблизительно) |

|---|---|

|

Всего параметров |

1,74 × 1011 (175 млрд) |

|

Вентилей на параметр (фиксированные 4 бита, амортизированные) |

~150 вентилей |

|

Всего вентилей |

≈ 2,61 × 1013 (≈26 триллионов вентилей) |

|

Транзисторы (4 вентиля на вентиль) |

≈ 1,05 × 1014 (≈100 триллионов) |

|

Параметры на слой |

≈ 1,812 × 109 |

|

Вентилей на слой |

≈ 2,72 × 1011 (≈272 миллиарда) |

|

Требуемое количество пластин (~2,6-транзисторы в масштабе Cerebras) |

≈ 40 пластин |

|

Требуемое количество чипов класса NVIDIA (~1×1011 транзисторов) |

≈ 1000 чипов |

Итоговые выводы

-

Жёсткое кодирование 4-битных весов в логике даёт очень большую экономию площади на параметр по сравнению с обычными MAC (примерно в 6–100 раз меньше на параметр в зависимости от исходного уровня), поскольку вы заменяете общие умножители на крошечную логику с постоянным умножением/ПЗУ и амортизирующие сумматоры.

-

Даже при этом, при параметрах 175 млрд полностью развёрнутая комбинационная ASIC всё ещё огромна — десятки триллионов вентилей / O(10¹⁴) транзисторов — и потребует множества кристаллов-вафлей или множества высокопроизводительных кристаллов.

-

Реалистичные инженерные подходы используют временное мультиплексирование, конвейеризацию, иерархии памяти на кристалле и вне его, а также сжатие модели (квантование, разреженность, факторизация) для практического вывода. Ваше предположение «полное отсутствие оперативной памяти» является крайностью и исключает основной практический рычаг, используемый в промышленности (весовые коэффициенты потоковой передачи), поэтому затраты на площадь остаются огромными даже после 4-битной оптимизации.

Автор: mahairod