Прошлая статья вызвала не такое обширное обсуждение, но очень важное, особенно про то что автор поверхностный и ничего не понимает в теме. Во второй части мы углубимся в каждый аспект и попробуем дать отравную точку для «Power Integrity» и чуть больше разберем проблемы, связанные с тепловыми расчетами. Своего рода «Handbook» для начинающего специалиста. Разговор будет длинным, и возможно прочитать за один раз его будет сложно.

Как и у любой большой темы начнем с того, что разобьём это на несколько блоков

-

PDN что это и с чем едят

-

Voltage drop

-

Impedance PDN

-

Разбор IPC

-

Тепловые расчеты

-

Stack-up

Давайте сразу оговоримся, что мы не будем затрагивать «Землю» в этом вопросе, хоть это очень важный и основополагающий элемент PI. Про него можно говорить очень много и долго, а нас, итак, ждем разговор не на пять минут.

Еще одна оговорка, здесь будет кучу англицизмов, слова целостнос��ь питания, падение напряжения, целевой импеданс будут даны только на английском. Автор стоит на том, чтобы использовать общепринятые в мире термины, на котором пишутся все статьи.

Ну и самая последняя оговорка, мы не сможем затронуть все темы, это невозможно и точно останется то, что я упустил или обговорил не в полном объёме. Прошу принять это и не гневаться, если будет большой спрос по определённой теме, я обязательно сделаю на эту тему разбор.

Начнем!

1. PDN что это и с чем едят

Начиная разбираться с PI, первое, с чем мы сталкиваемся это с PDN (Power Delivery Network). Что это такое? Тут процитирую Эрика Богадина:

Сеть подачи питани состоит из всех межсоединений в тракте подачи питания от модулей регулятора напряжения (VRMS) до цепей на кристалле. Как правило, к ним относятся плоскости питания и заземления на платах, кабели, разъемы и все конденсаторы, связанные с источником питания.

Назначение PDN заключается в том, чтобы

-

Распределять постоянное напряжение и мощность с низким уровнем шума на активные устройства, выполняющие всю работу.

-

Обеспечивать обратный путь с низким уровнем шума для всех сигналов.

-

Устранять проблемы с электромагнитными помехами (EMI), не увеличивая уровень радиационного излучения.»

PDN выполняет две фундаментальные функции, и провал любой из них автоматически приводит к отказам, которые часто ошибочно списывают на «плохую микросхему» или «шумный сигнал».

Первая функция — подача постоянного напряжения с допустимым уровнем шума. Любая цифровая или аналоговая схема потребляет ток не непрерывно, а импульсно. Если PDN не способна обеспечить локальный ток с достаточной скоростью, напряжение на кристалле проседает.

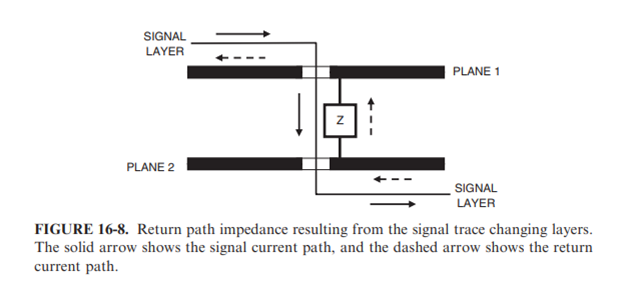

Вторая функция — обеспечение низкоиндуктивного обратного пути для сигналов. С точки зрения электромагнетизма, сигнал и питание неразделимы. Возвратный ток высокоскоростного сигнала всегда замыкается через ближайшую опорную плоскость. Если PDN разорвана, зашумлена или имеет высокую импедансную неоднородность, это немедленно проявляется в виде:

-

роста jitter

-

ухудшения eye-diagram,

-

увеличения EMI.

2. Voltage drop

В инженерной практике под Voltage Drop чаще всего понимают падение напряжения по постоянному току (DC IR‑drop) — то есть снижение напряжения питания вследствие сопротивления нашей PDN. Именно этот аспект исторически стал основой большинства стандартов, эмпирических графиков и «правил ширины дорожек».

Повторим формулы из прошлой статьи, но они самые базовые и необходимы нам

Закон Ома:

Сопротивление в медном проводнике можно вычислить по следующей формуле:

где

R – сопротивление;

ρ(T) – удельное сопротивление медного материала, зависящая от температуры проводника;

L – длина дорожки;

A – площадь поперечного сечения дорожки, W*Th,

где: W – ширина дорожки;

Th – толщина дорожки.

Удельное сопротивление медного материала, а следовательно, и сопротивление, является функцией температуры. Тепловой коэффициент сопротивления меди варьируется от 0,0038 (1/°C) до 0,0040 (1/°C) в зависимости от эталона. Поэтому, если сопротивление указано, оно всегда указывается при конкретной опорной температуре, обычно 20 ° C. Тогда удельное сопротивление при любой другой температуре определяется соотношением в Уравнении 2:

где:

T – интересующая температура

T0 – опорная температура

ρ(T) – удельное сопротивление при интересующей температуре

ρ(T0) – удельное сопротивление при опорной температуре

α – Температурный коэффициент удельного сопротивления при опорной температуре.

Если мы знаем сопротивление дорожки при какой‑либо температуре и хотим узнать сопротивление при любой другой температуре, просто подставляем R вместо ρ

На этом закончим короткую формульную справку заметив, что

Где P – плотность тока

Тогда мы получим зависимость от плотности тока

Зачем нам это необходимо?

Во многих современных микросхемах допуски на падения напряжения становится все меньше и меньше. Например, для современного АЦП AD4087, падения напряжения питания по 3.3В составляет 135 мВ, а по 1.1В допустимое падение составляет всего 55 мВ.

На практике DC voltage drop перестаёт быть абстрактной величиной и становится проблемой в следующих случаях:

-

низковольтные шины питани�� (≤1В), где допустимый запас по напряжению минимален;

-

высокотоковые потребители (CPU, FPGA, ASIC);

-

плотные BGA с ограниченным числом силовых выводов;

-

HDI-платы с тонкой медью и малыми сечениями;

-

длинные тракты питания между VRM и потребителем.

Во всех этих случаях потеря даже десятков милливольт по DC может съесть весь допуск по питанию. А если вы вдруг захотите поставить фильтры, например BLM, имеющим какое‑то значительное пассивное сопротивление, это задача становится еще сложнее. Да, она остаётся решаемой, поставить подходящий фильтр, подтянуть выходное напряжение, положить полигоны на нескольких слоях, но «на глаз» такие задачи уже решаются сложно (очень сложно).

Небольшое отступление, а вы знаете какая медь у вас используется? Точнее, сколько реально меди на каждом слое вы получаете?

Толщина меди регламентируется IPC-6012 и задает лишь минимальные значения, ниже которых изделие должно уходить в брак, но значений максимальных не дано. Это приводит к тому, что на практике толщина меди зависит лишь от производства и то насколько они пытаются получить запрашиваемую толщину.

Пример: запрашивая толщину меди ½Oz (18мкм) на внутреннем слое, IPC-6012 говорит, что минимальное значение толщины должно быть 12мкм (по 3 классу). Производство может сделать любую толщину не ниже 12мкм, то есть это может, как и 13мкм, так и 17мкм на разных слоях. На внешних слоях вообще разброс огромен, начиная от 38.4 мкм до примерно 60 мкм.

Толщина меди можешь значительно улучшить или ухудшить ситуацию с падением напряжением, так что советую поинтересоваться у вашего производителя, какие значения у них являются средними, ну или что будет лучше всего заложиться наихудший вариант, написанный в IPC.

Вернемся к падению напряжения. Как часто вы используете дорожки для проводки питания? Если у вас до 1А, я думаю это актуально в некоторых случаях, но «высокоточные» цепи обычно проводят полигонами, и вот тут вопрос, а достаточно ли вашего полигона?

Тут есть два с половиной подхода, первый залить полигон максимально всё на сколько это возможно. Второй, это прислушаться к опыту и логике, воспо��ьзоваться калькулятором и как‑то проложить полигон аппроксимируя значения.

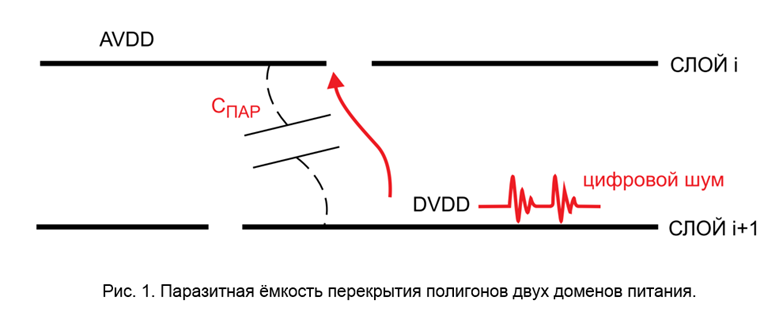

Проблема первого способа, это не эффективное использование свободного места на печатной плате, а также при выборе расположения двух питающих слоев в центре платы (что не очень хорошо, но это потом) возникает емкостная связь, которая служит каналом утечки высокочастотных шумов из одного домена в другой. Таким образом, например, шумы цифрового домена питания могут на внутренних слоях проникать в питание аналоговой части, приводя к неработоспособности чувствительной схемы. Это касается не только цифровых и аналоговых слоев питание, но и внутри каждого из этих видов тоже, это пример самого неудачного использования. Цифровые питание 3.3В может так же спокойно передать шум на цепь 1.8В, что может во многих случаях не так критично, но тот самый 1% потом будет сниться вам по ночам.

Проблема второго способа, отказы по причине высокого падения напряжения. Зачастую полигоны в плотных топологиях, в некоторых местах превращаться в «швейцарский сыр», что еще сильнее усложняет задачу выбора геометрии полигона, ведь понять какое там сечение невозможно.

Эти проблемы решает половинчатое решение, а именно реальное моделирование Voltage Drop после того или иного методов. Это позволяет сократить все негативные эффекты каждого из методов, так что остаётся лишь принять, то, что ближе к сердцу.

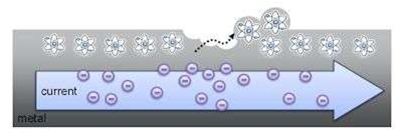

Давайте тоже оговоримся, что у полигонов есть одна большая проблема — это огромная среда для распрастронения шумов. Низкочастотные шумы питания распространяться по всему полигону итак же, как показано на предыдущем изображении, могут передаваться на сигнальные цепи, опорой для которых является этот полигон питания. Так же шумы могут передаваться от цепи к цепи, через как раз тот самый полигон питания. Еще вспомним, что если не проконтролировать, то у полигона могут получиться тонкие ответвления, которые могут быть антеннами, что как вы понимаете тоже не очень хорошо. Про решение этих проблем поговорим в последней части про stack‑up.

Хоть мы и не дошли до тепловых расчетов, но давайте кратко посмотрим еще раз на формулу падения напряжения.

Это температурно‑зависимая характеристика. Поэтому ВСЕГДА проводите анализ падения напряжения после температурного анализа или по максимальным климатическим условиям. Это убило не один проект, когда на столе с охлаждения все отлично, а в приборе не работает и начинаются гадания на кофейной куще.

3. Impedance PDN

Реальные цепи питания постоянного тока на печатной плате называют квази‑постоянными, потому что в физическом смысле напряжение и ток в них никогда не являются строго постоянным. Они всегда содержат временные и частотные компоненты, обусловленные как источником питания, так и нагрузкой, и самой структурой PDN.

В теории «постоянное напряжение» — это источник с нулевым внутренним импедансом и строго постоянным выходом во времени. В реальности на печатной плате такого источника не существует.

Практически все современные источники питания — это импульсные преобразователи (buck, boost, LDO с импульсным предрегулятором и так далее). Они формируют выходное напряжение за счёт коммутации ключей с конечной частотой переключения. Даже если на выходе стоит LC‑фильтр, он лишь ослабляет, но не устраняет полностью переменную составляющую.

В результате на выходе источника всегда присутствуют:

-

низкочастотные пульсации (ripple) на частоте переключения и её гармониках;

-

высокочастотный шум от фронтов ключей;

-

паразитные резонансы выходного фильтра и разводки.

С точки зрения математики напряжение питания выглядит так:

То есть DC — это только среднее значение, а мгновенное напряжение всегда меняется во времени. Для аналоговой схемы это проявляется как шум, для цифровой — как джиттер и просадки питания. Поэтому уже на уровне источника питание перестаёт быть строго постоянным и становится квази‑DC.

Нагрузка потребляет ток не постоянно, а импульсами

Даже если источник был бы идеальным, нагрузка делает питание квази‑постоянным. Цифровые микросхемы не потребляют ток равномерно. Основной ток возникает:

-

в моменты переключения логических элементов;

-

при зарядке и разрядке внутренних ёмкостей транзисторов;

-

при одновременном переключении большого числа выходов.

В результате ток потребления имеет импульсный характер и может изменяться на порядки. Формально средний ток может быть, например, 200 мА, но мгновенный ток в короткий момент времени — несколько ампер, например при запуске моделирования на вашем ПК. Опять же оговоримся, что это не всегда чисто схемотехническая причина, грамотно написанный код может в какое‑то степени решить эту проблему, постепенной нагрузкой процессора.

Любая цепь питания имеет ненулевой импеданс. Поэтому при быстром изменении тока возникает мгновенное отклонение напряжения:

-

резистивная составляющая: ΔV = I · R

-

индуктивная составляющая: ΔV = L · di/dt

Особенно критична именно индуктивность, потому что di/dt у цифровых микросхем очень велик. Даже несколько пикогенри дают измеримые провалы напряжения, которые заметно влияют на ваши сигналы.

С инженерной точки зрения это означает, что питание должно рассматриваться как динамическая система, которая должна успевать подстраиваться под мгновенные запросы тока нагрузки. Если она не успевает — появляются просадки, ground bounce, ошибки логики и сбои.

Импеданс

Там, где есть индуктивная и резистивная составляющая всегда появляется импеданс. Так как же он влияет на наши сигналы.

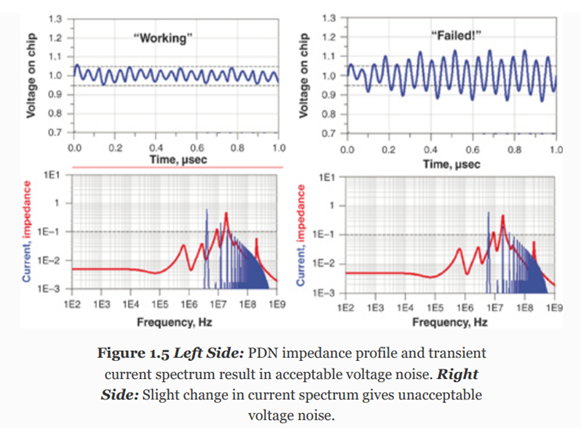

В левой части рисунка снизу показан спектр переходного тока, профиль импеданса PDN и результирующий шум напряжения на шине питания сверху. Эта комбинация пиков спектра тока и пиков импеданса приводит к приемлемому уровню шума. Справа показан тот же профиль импеданса, но с немного другим алгоритмом микрокода, управляющим теми же затворами на немного другой частоте. Пик спектра тока перекрывает более крупный пик импеданса, создавая шум напряжения на шине питания, превышающий допустимый предел.

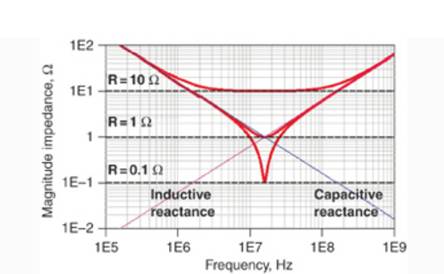

Часто проблема не в том, что у вас мало емкости, а в том, что индуктивность соединений между разными типами конденсаторов создает «дыру» в импедансной характеристике. Эта «дыра» (антивыброс, anti‑resonance) может быть даже хуже, чем высокий импеданс самого по себе конденсатора.

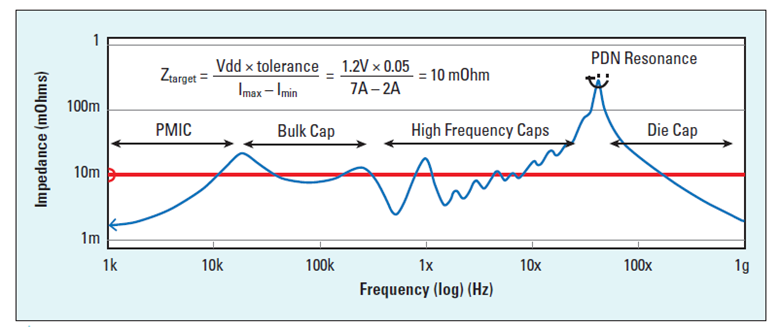

Мы вроде бы разобрались, что нам необходим определенный профиль нашего импеданса, но как его достичь. Для этого был придуман «Target Impedance». Это чисто инженерная приближение, вот что про него пишет Эрик Богадин:

Целевой импеданс является полезным показателем качества PDN. Это хорошее приближение к цели проектирования для надежной конструкции PDN. Окончательная оценка надежности конструкции PDN будет получена на основе моделирования переходных процессов всей PDN и форм сигналов переходного тока

Target Impedance — максимально допустимый импеданс нашей системы питания.

Формула, с которой всё начинается:

Где:

V — номинальное напряжение.

a — допустимое отклонение напряжения/

ΔI — максимальный скачок тока, который представляет собой разницу между минимальным и максимальным током потребления.

Пример: Напряжение 1.0В, допуск 5%, максимальный ток потребления 2А.

Так как мы изначально не можем понять какой скачок тока может быть в нашей PDN, Эрик Богадин предлагает брать максимальный ток потребления и поделить его на два и сказать, что это тот самый скачок. Это не универсальное правило, но для большинства случаев это может быть актуально. Давайте тогда посчитаем:

Получается наша PDN‑система должна иметь импеданс менее 50 мОм вплоть до самых «высоких частот». А что такое эти ваши «высокие частоты»?

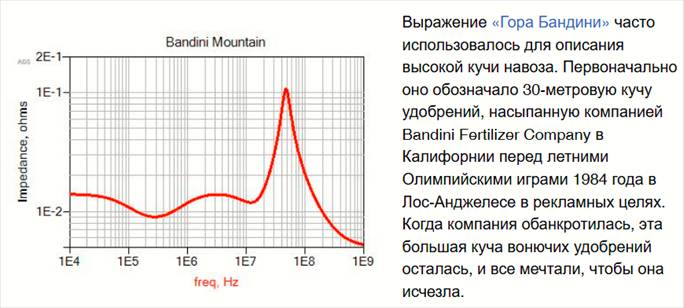

Если открыть типичные статьи и даже программы по моделированию, они предлагают смотреть импеданс PDN от 10кГц до частот 200–300 МГц. Почему так? Во всем виновата большая куча г@вна и я не шучу!

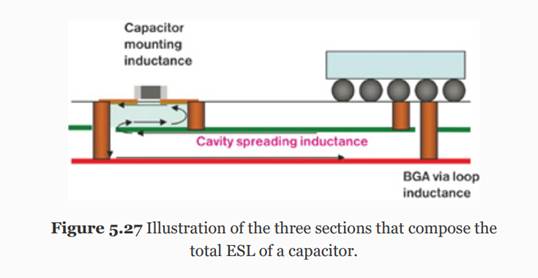

Профиль импеданса от контактных площадок микросхемы, особенно при низких частотах, зависит от того, что подключено к другой стороне выводов корпуса. Если взять «самый лучший случай», когда импеданс PDN платы минимально возможен, то есть короткое замыкание, контакты микросхемы видят параллельно соединенные емкость развязк�� на кристалле и индуктивность выводов корпуса. Сочетание этих двух элементов создает параллельный резонанс, который является наиболее важной характеристикой в PDN.

Когда профиль импеданса PDN рассматривается с точки зрения кристалла, пик параллельного резонанса удивительно напоминает гору. Поскольку его роль в PDN настолько заметна, Стив Уир сразу же увидел эту связь и в шутку назвал этот пик импеданса «горой Бандини», что является очень точным описанием. Пиковое значение импеданса горы Бандини в основном связано с коэффициентом q LC‑резонатора, который зависит от ESR двух элементов. ESR выводов корпуса и ESR конденсатора на кристалле часто способствуют высокому коэффициенту q для резонансного пикового импеданса со значениями, приближающимися к 1 Ом.

На плате мы никак не сможем от него избавиться, его существование обусловлено корпусом микросхемы и его соединением с платой, и может быть изменено только на этапе проектирования самого корпуса. В случае разработки схемы и топологии нам необходимо добиться целевого импеданса PDN для частот ниже частоты «Bandini Mountain».

Важный комментарий, частоту «Bandini Mountain» и вид этого выброса зачастую ни один производитель не дает, но он может указать рабочие частоты, на которых стоит производить измерения PDN.

Другими словами, нам необходимо сделать максимально плавный профиль импеданса ниже target impedance на всей рассматриваемой частотной области до Bandini Mountain

Профиль импеданса

Давайте коротко поговорим про профиль импеданса. У многих в книгах этому отводиться десятки страниц, а мы попробуем уложиться в пару абзацев.

Если профиль импеданса PDN, видимый со стороны контактных площадок ИС, представляет собой плоский профиль импеданса от постоянного тока до самых высокочастотных компонентов переходного тока, и мы поддерживаем плоский импеданс PDN ниже целевого импеданса, то наихудший случай шума напряжения из‑за динамического тока на контактных площадках шины ИС будет меньше максимально допустимого шума напряжения.

Хотя достижение плоского профиля импеданса является важной задачей, во многих случаях его реализация во всем диапазоне частот слишком затратна. В профиле импеданса могут наблюдаться пики. Они обычно возникают на границах между различными элементами межсоединений, такими как

-

между VRM и развязывающими конденсаторами

-

между объемными развязывающими конденсаторами и конденсаторами MLCC

-

между индуктивностью выводов корпуса и емкостью кристалла

Содержимое, созданное искусственным интеллектом, может быть неверным.

Мы уже кротко поговорили про VRMs и про потребителей и их влияние (Bandini Mountain), давайте так же коротко про профиль конденсаторов и общий профиль.

Профиль, создаваемый реальным компонентами (будь это конденсатор, VRM или микросхема), состоит из трех составляющих, емкостной, резистивной и индуктивной. Резистивная отвечает за то, на сколько низкий пик резонанса возможен. Емкостная и индуктивная, отвечает за положение нашего «V‑профиля». (Формулировки максимально упрощены, на самом деле все не так, давайте простим это автору, он хочет максимально впихнуть невпихуемое)

Положение данного профиля будет находиться на резонансной частоте, которую легко посчитать

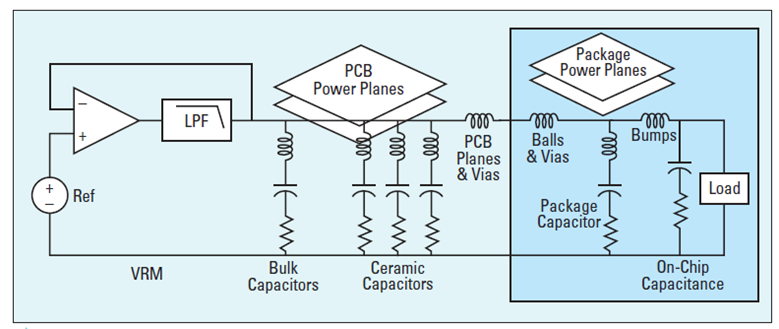

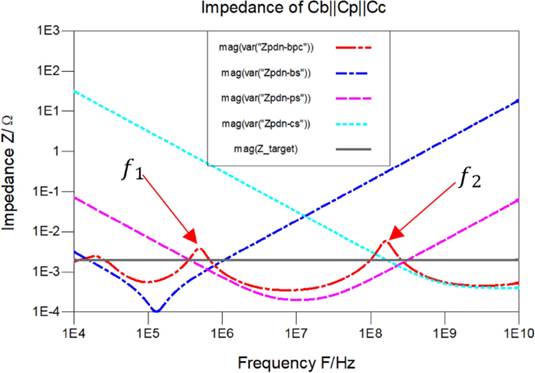

А теперь коротко о том, что формирует тот самый полный профиль. Профиль создается контурами. Каждый контур имеет свой профиль «V», и складывая совокупность этих контуров, мы получаем как раз наш профиль.

Красная линия показывает импеданс системы, остальные линии показывают составляющие каждого контура

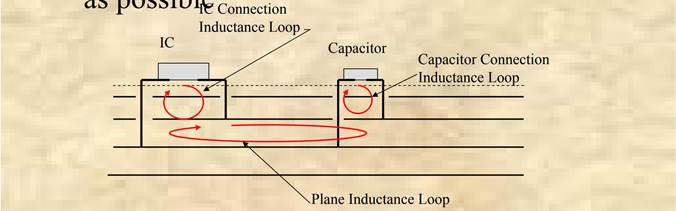

Ниже показано как именно формируются эти самые контура. Это упрощенная модель и на самом деле стоит понимать, что контур строиться от каждого «источника» до приемника. В данном случае при резком росте потребления энергии, конденсаторы являются «источниками». Еще энергия запасается самой печатной платой, так как между слоями питания и заземления существует своя емкость, которую необходимо учитывать.

Так же можно встретить вот такие изображения, где наши контура разбивают на несколько. На сколько это необходимо вопрос дискуссионный, но это то, о чем стоило бы сказать.

4. Разбор IPC

Все мы любим четкие правила, а еще больше IPC. Давайте разберем два важных IPC (IPC-2221 и IPC-2152) с точки зрения PDN, а именно дорожек/полигонов для нашего питания, опустив некоторые другие вещи.

IPC-2221

Я хочу надеяться, что все читали IPC-2221, так как это основной стандарт для печатных плат. И, надеюсь, все знают, что там есть четкие правила по поводу ширины дорожек. Они выглядят так (в ред. 1998 г.):

«6.2 Conductive Material Requirements The minimum width and thickness of conductors on the finished board shall be determined primarily on the basis of the current-carrying capacity required, and the maximum permissible conductor temperature rise. The minimum conductor width and thickness shall be in accordance with Figure 6-4 for conductors on external and internal layers of the printed board»

где «shall» это обязательное выполнение

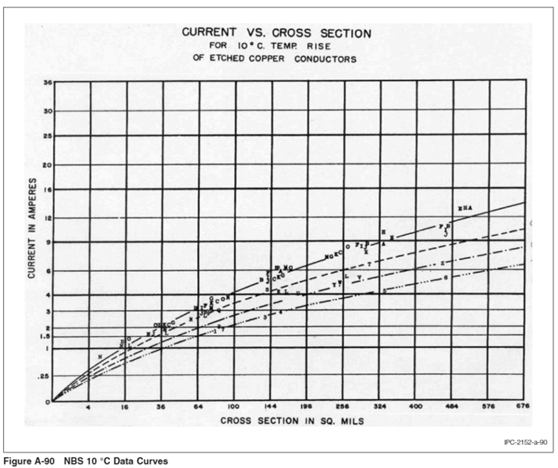

Вот отсюда начинаются все проблемы. Я уже рассказывал про проблемы приведенных графиках и откуда они у нас (читайте в прошлой статье), единственное что добавлю, это исторический график того самого отчета NBS, который потом перепечатывали и брали за истину

Использование слова «shall» обязало инженеров по всему миру придерживаться этих графиков, так как это общепринятый стандарт, который как показало время оказался полной ерундой.

IPC-2152

Давайте начнем с названия, которые вводит в заблуждение «Standard for Current Carrying Capacity in PCB Design». Чуть забегая вперед, мы поймем, что стандарт можно было назвать «Зависимость температуры от токовой нагрузки в 1% случаев в вашей практики», так как реально он никак не дает понимание о пропускной токовой нагрузке и заставляет инженеров свято верить в этот стандарт.

Новый стандарт, должен был решить проблему чрезмерности и дать ясности как действовать с современными многослойными печатными платами. И он её решил, но была одна проблема.

Проблема это заключается в том, что этот стандарт никто не читал (автор оценивает людей, читающих данный стандарт в 5–10% в отрасли). Это объясняется довольно‑таки легко. Во‑первых, IPC членская структура, за которую необходимо платить очень большие деньги ежегодно, что не могут себе позволить маленькие и средние компании. А во‑вторых, отсутствия досконального изучения всех стандартов. У IPC десятки стандартов по печатным платам на сотни страниц, которые сложно держать все в голове и четко понимать, какие из них реально нужны, а какие нет. Поэтому большинство ограничивается стандартов IPC-2221, который зачастую ну уж очень обобщённый.

Вернемся к стандарту. Исправил ли он все проблемы предыдущего? Скорее нет, чем да. В новом стандарте уточнили некоторые момент, за счет большего количество опытов и компьютерных симуляций, но самое важное, что они сделали это убрали слово «shall» и написали про ограниченность всех предоставляемых диаграмм. Давайте ознакомимся с этими ограничениями, я подобрал самые важные на мой взгляд (цитаты даны в оригинале без перевода, для точности формулировок)

Что пишет IPC по поводу ухудшений параметров от тока:

«Current-Carrying Capacity The maximum electrical current that can be carried continuously by a conductor, without causing an objectionable degradation of electrical or mechanical properties of the product»

Цитата, что IPC не учитывает все факторы:

«The mounting of the PB, environment (air, vacuum, forced air), copper plane layers, the components that the conductor is connected to, and length of the conductor are a partial list of the things that can impact the conductor temperature rise. It is not feasible to assemble charts that address all of these concerns. Therefore, charts are presented that take into account a wide spectrum of design concerns that bound most PB designs used in still air and vacuum environments»

Про параллельные проводники

«For isolated conductor applications the charts in Section 5 may be used directly. For groups of parallel conductors, if closely spaced, the temperature rise may be found by using an equivalent cross-section and an equivalent current. The following apply to parallel conductors:

1) Parallel conductors refer to adjacent conductors on the same layer and on adjacent layers.

2) Adjacent conductors within 25.4 mm [1.0 in] can affect the temperature rise. This means that, for many PBs, all conductors are thermally linked and need to be considered as such»

Про то, что взято за основу плата без проводников

«The charts included in this document represent copper conductors in a polyimide or FR-4 epoxy resin based PB without copper plane layers. This configuration is consistent with IPC-TM-650, Method 2.5.4.1»

Про то, что одни таблицы не может оценить всё:

«With such a broad range of PB construction, materials, and operating environments, a single conductor-sizing chart cannot be expected to describe the temperature rise of a conductor as a function of current for all PB designs. Fine line and space, heavy copper, single-layer PBs and multilayer PBs all constitute different configurations in which conductors with the same cross-sectional area vary from 10 to 100 °C or more for the same amount of applied current»

Про переходные отверстия

«A.3.4 Vias The cross-sectional area of a via should have at least the same cross-sectional area as the conductor or be larger than the conductor coming into it. If the via has less cross-sectional area than the conductor, then multiple vias can be used to maintain the same cross-sectional area as the conductor. The cross-sectional area can be calculated based on the barrel diameter and the plating thickness. The plating thickness can be assumed to be 0.0178 mm [0.0007 in] thick unless otherwise defined. Figure A-11 illustrates the cross-sectional area of a via»

«A.3.4.1 Conductor to Via to Plane If a conductor is connected to a via and the via is connected to a plane, the plane will conduct heat away from the via and the via will run cooler than the conductor»

«A.3.4.2 Microvia Microvias react to temperature rise due to current in the same manner as a through-hole via. The cross-sectional area is the parameter that relates to a current level and temperature rise»

Про то, что используются при компьютерные модели для расчета нагрева с полигоном

«A.4.6.1 Single Plane Computer thermal models were created and correlated with conductor heating data collected using 1.79 mm [0.070 in] thick polyimide test vehicles. After correlating the models², layers of copper, or plane layers, were added to the models. Results from those models were used to develop charts that represent conductor temperature rise as a function of current for conductors in PBs with layers of copper»

Про факторы, влияющие на распределения тепла

«A.5.1 Heat Transfer from a Conductor Heat transfer from a conductor is fairly complex when all aspects of a design are taken into consideration. The PB thickness, copper thickness, length of conductor, number of layers, PB material, environment (earth, vacuum, forced air, high-altitude), vias, odd shaped copper planes, multiple layers, “Swiss-cheese effect” due to vias in planes, mounting configurations, airflow, components, radiation and convection are all variables that impact the temperature rise of a conductor in a PB. These variables don’t all affect the temperature rise equally and the key is to understand what the primary and secondary factors are that affect the conductor temperature rise»

Про изрезанные полигоны питания:

«A.5.3 Odd Shaped Geometries and Swiss-Cheese Effect High current is often applied to copper planes that deliver the power to various locations in the printed design. It is not uncommon for these copper planes to be odd shaped geometries. The simple conductor sizing charts become limited in their use for these applications»

Про ограничение использования для «небольших» плат

«A.5.4 HDI Fine line and space, thin copper and small PBs create new design challenges. When PBs get smaller than 76.2x 76.2 mm [3.0 x 3.0 in], the current carrying capacity decreases. In addition, as PB thickness decreases the current carrying capacity decreases. The charts in IPC-2152 are limited to PB sizes larger than 76.2 x 76.2 mm [3.0 x 3.0 in]»

Скажем честно, оговорок очень много, но еще больше там графиков, а именно 120, который соответствует каждый своему случаю. Не мало скажем честно и начнем чуть больше понимать людей, которые не изучали этот стандарт.

Насколько нам это реально нужно?

Это вопрос сложный и открытый и надо рассказать, про то, что на самом деле повышение температуры до 100 градусов и выше ничего не сделает с вашей дорожкой.

Если рассматривать вопрос про то какие дефекты возникают, при высоких температурах, то их два основных и два побочных.

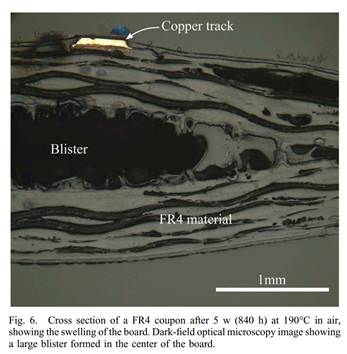

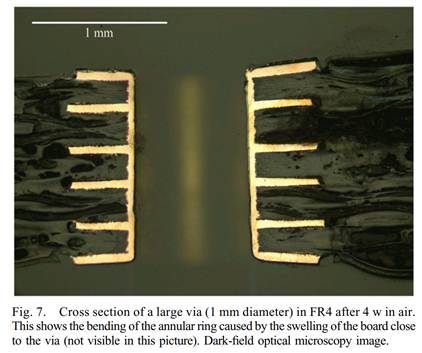

К основным я отнесу следующие: увеличение КТР диэлектрика и термоокисление. Увеличение КТР связанно со свойствами смолы, которая при увеличении температуры меняет свои значения КТР и чем ближе к температуре стеклования (Tg) тем сильнее меняется. Например, для стандартной FR4, при температуре выше Tg, КТР материала резко возрастает (от 40 до 240 ppm/К в направлении Z), что может ускорить расслаивание.

Термоокисление тоже является важным фактором, из‑за диффузии кислорода в смоле. Смола резко наберет воду и что приведет к разбуханию. Но стоит сказать, что это довольно кратковременное явление, ведь сразу после этого, наш диэлектрик начнет «худеть» из‑за испарений внутри и высвобождения кислорода.

Теперь к побочным дефекты: электромиграция и CAF. Про них очень коротко

Элекстромиграция это постепенный перенос атомов металла в проводнике под действием импульса от потока электронов при высокой плотности тока. Со временем это приводит к образованию пустот и наплывов металле, что вызывает рост сопротивления и, в итоге, отказ проводника или межсоединения. При температурах примерно 150 градусов и плотности тока 1.82*10^4 А/см2 (100 А/мм^2) в соединениях через 1154 часа работы начали происходить первые отказы. Данные были получены на межсоединениях внутри транзисторов. Информации по поводу того, как это влияет на дорожки печатных плат очень мало.

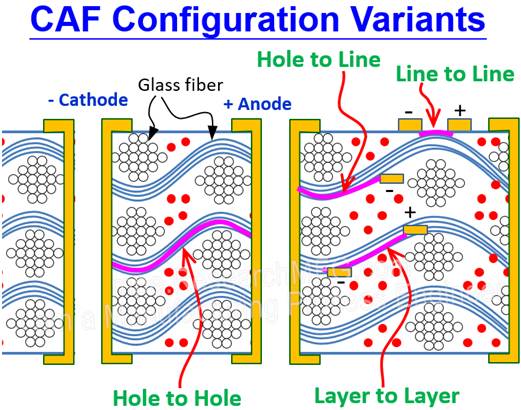

CAF (Conductive Anodic Filament) — это электрохимический процесс, приводящий к образованию проводящих металлических нитей (меди) внутри печатной платы между проводниками (обычно от анода к катоду). Зачастую это происходит в переходных отверстиях. Для возникновения этого эффекта выделяют 3 основных условия: влажность, разность потенциалов и структура. Как мы можем понять, во влажной среде, а еще и при росте температуры выше 100 градусов, смола резко начинает впитывать влагу из окружающей среды, что резко повышает риск. Так же нам необходима большая разность потенциалов, в условиях разницы в 1В, ничего не будет, но десятки, а то и сотни вольт добавляют факторов риска. Ну и структура, близкое расположение переходных отверстиях (особенно в HDI) и использование стеклотекстолитов, вдоль волокон которых как раз образуются нити.

Хоть все исследование говорят, что это в значительной степени происходит при температуре выше 200 градусов и при долго воздействии, но сказать об этом стоит.

Краткое заключение. IPC отлично подойдет для 2-ух, максимум 4-ех слойных плат с небольшим количеством дорожек (где нет полигонов). Во всех остальных, это ужасно странный инструмент, который больше путает. Понятное дело не стоит делать дорожки, на которых прирост температуры будет +50 градусов, ведь она же не выгорит и не отвалиться. Да не выгорит и не отвалиться, но есть другие эффекты как электромиграция, которая со временем разрушит ее, да и общие климатические прибора вряд ли будут удовлетворимы.

Лично мои рекомендации, если уж и считать прирост держать его в приделах до +5 градусов и плотностью тока менее 100 А/мм^2 для конкретной дорожки, а дальше моделировать.

5. Тепловые расчеты

Это моя любимая часть, потому что на ней видна, что никто не пытался осознать эту тему.

Начнем с напоминания, о факторах, влияющих на температуру, начиная с голой платы, заканчивая смонтированной.

Главными факторами, влияющими на температуру в печатных платах (без учета компонентов):

-

Наличие полигонов меди:

Добавление сплошного полигона земли на нижний слой д��ухслойной платы снизило пиковую температуру на 30% (при токе 5А). Это связано с тем, что медь имеет высокую теплопроводность и способствует распределению и отводу тепла.

-

Толщина платы:

В двухслойной плате без полигона на нижнем слое уменьшение толщины платы с 1,464 мм до 0,5 мм привело к заметному изменению температуры (увеличило нагрев). Это объясняется уменьшением объема диэлектрика с относительно высокой теплопроводностью (0.3 Вт/м·К) по сравнению с воздухом (0.03 Вт/м·К).

Однако, при наличии полигона на нижнем слое изменение толщины платы не оказывает значительного влияния, так как два фактора уравновешивают друг друга:

a) Уменьшение толщины уменьшает объем диэлектрика с более высокой теплопроводностью.

b) Уменьшение толщины сокращает путь до меди, которая имеет очень высокую теплопроводность (400 Вт/м·К).

-

Количество слоев

С увеличением слоев увеличивается теплопроводность за счет большего количества меди и уменьшением расстояния между ними (если брать при одинаковой толщине).

-

Размер печатной платы:

Увеличение размера платы в 2 раза привело к снижению температуры, а уменьшение — к повышению. Это связано с тем, что большая плата имеет большую поверхность для рассеивания тепла.

-

Использование Thermal Vias

Для большинства случаев оптимальное количество thermal vias — от 2 до 4. Добавление большего числа дает незначительный прирост эффективности и может чрезмерно усложнить трассировку.

Теперь перейдем к плате, где компоненты тоже выделяют своё тепло. Начну эту часть с истории.

В одной из компаний всеми расчетами тепла занимался опытный конструктор и делал это в SolidWorks (в расширении Flow Simulation) и исторически это начали делать именно конструктора и именно в SolidWorks. Это было удобно ведь эти платы можно было считать сразу в корпусах и с радиаторами. По мере моего изучения моделирования и понимания необходимости совместного моделирования (тепла и питания/сигналов), чтобы не бегать просить посчитать мне тепло, а потом как‑то это аппроксимировать, я сам начал это изучать. Так как я пользовался ADS, там была встроенный Thermal Simulator, который я не без проблем, но быстро освоил. И вот я довольный прихожу к конструктору, говорю, что нам надо добавить радиатор, а он говорит, что по его расчетам ничего не надо. Мы смотрим, а у нас разница почти в 2 раза…Понятное дело, я пошел искать у себя ошибку и разбираться дальше, еще не осознавая, какой веселый путь надо пройти.

Давайте сразу сделаем оговорку. Мы не учитываем в этом разговоре выделяемое тепло от наших дорожек. На практике в больших многослойных платах, они дают +5 градусов, пусть это будет наша погрешность. Ну и все дальнейшие методы будут сделаны на основе моделирований в ADS.

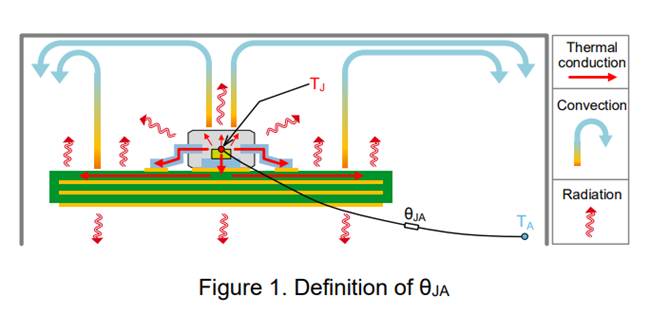

Начнем с азов. Тепловое сопротивление (θJA — junction‑ambient) — это количественная оценка того, насколько трудно проводить тепло. Тепловое сопротивление представляет собой отношение разности температур между двумя заданными точками к тепловому потоку между этими двумя точками (количество теплового потока в единицу времени). Это означает, что чем выше тепловое сопротивление, тем труднее проводить тепло, и наоборот.

Единицей измерения теплового сопротивления является К/Вт или °С/Вт. Хотя K и °C различаются по своим абсолютным значениям (0 K = -273,15°C), их можно рассматривать как равнозначные по относительным температурам (K = °C).

Давайте рассмотрим схематичное изображение распределения тепла от компонента.

Мы можем заметить, что тепло у нас уходит по 3 путям:

-

через пины и термопад на плату, а потом в окружающую среду

-

через верхнюю часть корпуса в окружающую среду

-

через излучение (будем это опускать, так как это незначительная часть энергии)

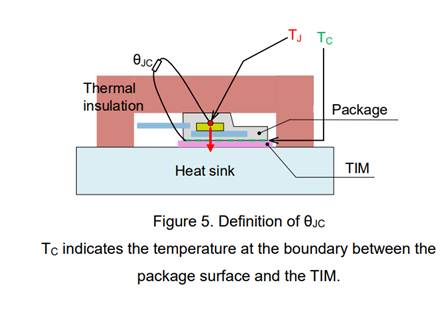

Правда так? Ну на самом деле нет, вот более правильная схема

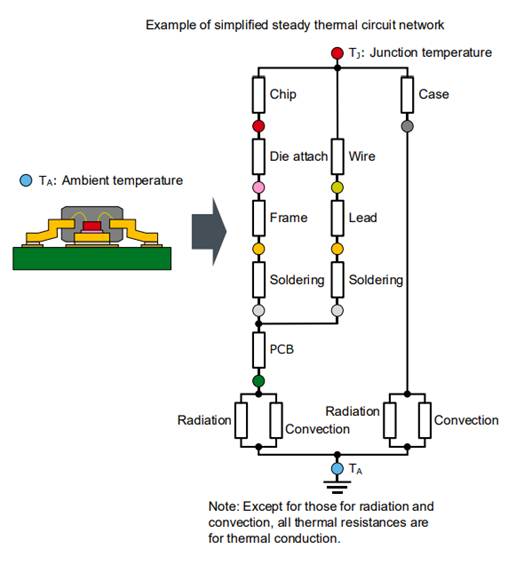

Давайте разберемся. Компонент не греется сам по себе, само выделение тепла происходит на чипе. Дальше идет длинная цепочка передачи этой энергии. Один из путей от чипа к разварке, от нее к пинам, к припою, потом на плату и потом только в окружающую среду. И как вы можете понять это у каждой этой «линии передачи» передачи, есть свое тепловое сопротивление.

Именно поэтому использование θJA неудобна для точных расчетов. Зачастую нам необходимо понять на сколько нагреется тот или иной компонент, а его нагрев полностью зависит от теплового сопротивления, который не дает энергии уходить в открытое пространство. Если оно задано хоть как‑то, то и результат будет соответствующим.

Именно поэтому начали использовать более репрезентативные параметры, а именно θJt (junction‑top) и θJb (junction‑bot). Это тепловые сопротивления не одинаковые, так как чип зачастую расположен ближе к bot, да и передача тепла через пины идет более активно. Но зачастую мы все же встретим θJc (junction‑сase) и θJb (junction‑board), где θJc это зачастую сопротивление к bot case, а θJb (junction‑board) сопротивление от чипа к площадке.

Так же стоит поговорить о тепловом сопротивление материалов самой печатной платы. Давайте сейчас забудем, что тепловое сопротивление грамотнее писать по осям (это всплывет потом в SolidWorks) и примем какое‑то среднее значение.

Для материалов не используются параметр теплового сопротивления, там используется тепловая проводимость (это обратный параметр). Так, например для меди значения проводимости будут от 350W/mK до 450W/mK, а у типичного диэлектрика от 0.25W/mK до 0.4W/mK. Мы сразу видим, что проводимость меди на порядки выше, а значит отводить тепло оно будет лучше.

От теории к делу

Мы решили посчитать выделение тепла, например AD9253, и скажем, что мы посчитали и она выделяет ну пусть 1 Вт. Что делать дальше?

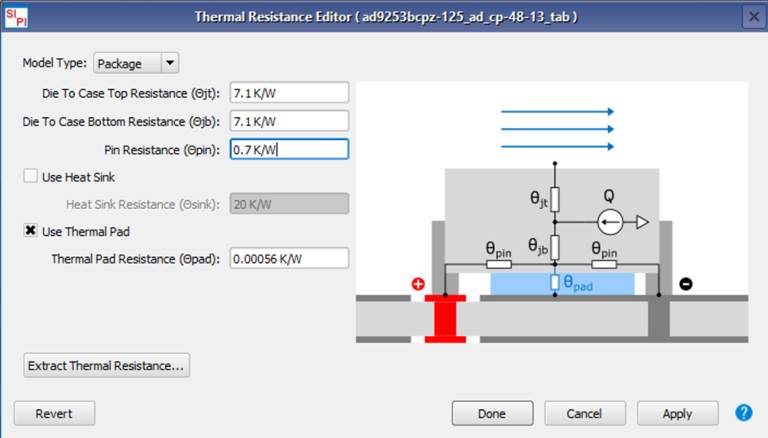

Как мы уже знаем выделяет не сам компонент, а его чип. Тогда нам необходимо знать его тепловое сопротивление. Зачастую она написана в документации, что дает нам новости для радости. Переходим в ADS и заполняем.

Нам необходимы θJt (junction‑top) и θJb (junction‑bot) и θJpin (junction‑pin). С первыми двумя все более‑менее легко, и мы хоть как‑то, находим это в спецификации, с последним уже сложнее, так как этот параметр не пишет никто.

Стоит сделать отступление и сказать, что, например тот же ADS сам умеет генерировать эти сопротивления, но о их точности можно только гадать. Зато у компонентов на чьи корпуса производитель не дал тепловые сопротивления или дал не полные этим можно и нужно воспользоваться

Мы получаем следующие параметры:

θJt = θJc = θJb = 7.1;

θJpin = θJb (junction-board)- θJc = 7.8-7.1= 0.7.

Thermal Pad идет сразу на общий полигон, поэтому у него сопротивление почти 0

Близко ли это к правде? Нет!

Давайте обратимся к методике измерений этих параметров (очень кратко). Для измерений используется стандартная печатная плата по JESD51-2. И используют примерно такую установку.

Как вы понимаете погрешностей в измерениях здесь куча, так еще и многое зависит сопутствующих факторов, но мы допустим, что это все верно и значения точные.

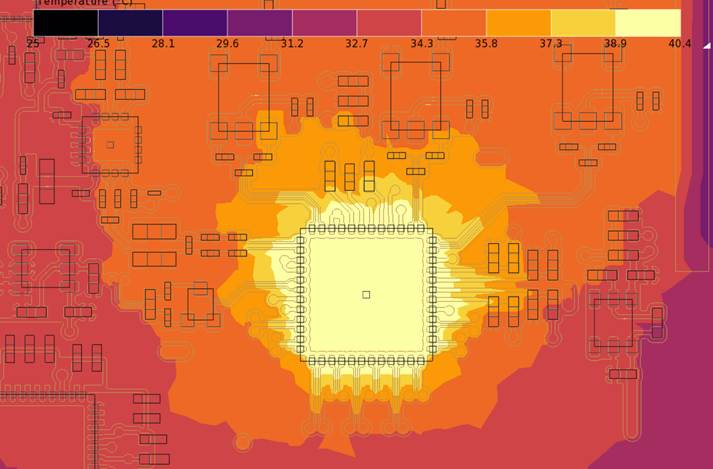

И вот все модели заданы (опустим как мы задавали параметры диэлектриков и меди) запускаем моделирование в ADS и видим наше распространение тепла и нагрев, то куда и как тепловые потоки идут по меди и диэлектрику.

И вот он переломный момент, когда мы переходим к SolidWorks.

Мы загружаем нашу Step модель и тут несколько вариантов:

-

Модель выгружена без слоев меди, чтобы она быстрее грузилась

-

Модель с медью, но без переходных отверстий (Mentor Graphics может максимум только так)

-

Модель полностью повторяет печатную плату

Очевидно, уровень полученных результатов от каждого из вариантов. Ну примем самый ужасный вариант, где у нас есть просто прямоугольник и на нем такие же прямоугольные компоненты.

Встает вопрос, а как задавать параметры материала печатной платы. Ответ простой — выбрать этот материал в списке. Что это за материал, откуда у него такие параметры, одному разработчику известно. Хорошо, надеемся, что это не скажется (еще как скажется), переходим к компонентам. Ну тут два варианта, или там есть какие‑то стандартные модели (параметры которых ну не вызывают доверия) или задавать самим, а как?

Там в отличии от ADS задается мы в SolidWorks параметр проводимости по двум осям. Мы об условились что возьмем что‑то среднее, и давайте возьмем θJc (junction‑сase), тогда проводимость как обратный параметр к сопротивлению получить не сложно.

И вот мы задали все параметры и параметры симуляции приблизили к ADS (температуру окружающей среды и сетку) и получили лажу. Мы получили параметры, которые никак не стыкуются с реальностью. Мы сделали миллион допущений, что привело нас к провалу.

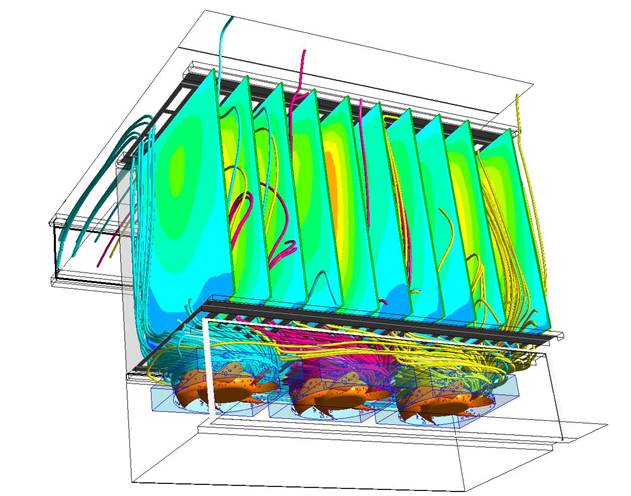

Значит ли, что SolidWorks нельзя использовать для анализа тепловых эффектов прибора? Конечно же нет. Это лишь значит, что для анализа пиковых температур на печатной плате, этот инструмент не подходит, те допущения, которые мы делаем критически сказываются на работоспособности. SolidWorks может помочь вам именно в сборках, когда у вас появляются корпуса, радиаторы и большое количество плат, то есть все то что нельзя сделать в специализированном софте для моделирования печатных плат (HyperLynx, ADS и так далее).

Даже при тех допущениях на уровне сборок он будет показывать приемлемый результат, так как выделение тепла не меняется, меняется только распределение в пространстве, а на уровне сборок значимость этих погрешностей уменьшается.

Что же делать? Первый вариант, смириться. Даже в этой схеме вы получите удовлетворимый результат, а если вы методом подгонки значений сможете получить в SolidWorks примерно, то же самое, что получили в ADS, то вообще радость. Второй, начать пользоваться такими программами как Ansys Acepak. Сразу же можно сказать, что это вряд ли будет, если уже лицензия на ADS стоит очень дорого, что не каждая компания готова себе это позволить, то Ansys Acepak стоит еще больше, так и вычислительных мощностей вам надо немало. Но это уже тяжелая артерия, где платы не аппроксимируются, а учитываться полностью со всей медью и переводками. Теплопроводность можно задавать к каждой грани и добавлять любые конфигурации корпусов и вообще работать одно удовольствие, если у вас для этого есть отдельный сервер.

6. Stack-up

Для начала начнем с типовых плат и их проблем. Я бы в целом мог ничего не писать, а просто сказать, чтобы все посмотрели мастер‑класс Эрика Хартли для Altium, где он прекрасно все рассказывает, но давайте разберемся тут.

Сразу давайте ответим на вопрос, чем отличается типовые решения от других. Все типовые решения — это «толстый» центр и «тонкие» препреги снаружи. Для 4-ех слойной платы, stack‑up будет состоять из тонких препрегов снаружи и очень толстого ядра внутри. И как обычно выглядит планировка слоев этой платы SIG‑GND‑PWR‑SIG. В этот момент мы должны схватится за голову и сказать какой ужас. Между слоем GND‑PWR для 1,5мм плат примерно 1,1мм диэлектрика. Это ужасный выбор планировки слоев. Индуктивность внутренних контуров питания, будет иметь огромные значения, а излучения, создаваемые этим контуром, создает огромные помехи.

Да, использование типовых решение допустимо для простых устройств и плат, где все шумы и излучения никак не влияют на работу прибора. Но использовать данные решения в проектах, где частота работы интерфейсов превышает 500МГц приведет к большим проблемам.

Всяких разных вариантов много, но вот важные вещи, которые, по мне, стоит учитывать при выборе Stack‑up, которые я бы назвал «Key point» с точки зрения PI.

1. Расстояние между слоем Земли и Питания, пытайтесь его минимизировать, для минимизации индуктивности

2. Избегайте расположение цепей Питания разного напряжения друг под другом, особенно когда одна питает цифровую часть, а другая аналоговую.

3. Заливайте полигонами «Земли» все свободные пространства. (Объяснения у Рика Хартли смотрите)

4. Если для высокочастотных сигналов опорным слоем является слой питания, важно использовать максимально тонкие диэлектрики и закорачивать плоскость питания и «GND» конденсаторами (без разницы на емкость, главное меньшая индуктивность).

5. Слои питания должны находиться максимально близко к заземляющей плоскости, ближе, чем ближайшие слои питания и сигналов. Чтобы иметь инженерную прикидку, то до ближайшего полигона Земли должны быть расстояние в два раза меньше, чем до ближайшего сигнального или другого слоя питания.

Заключение:

Разработка топологии — это легко, в чем вы только что и убедились, увольте всех топологов, а на их место поставить ИИ и пусть эти людишки умрут с голода, бездельники. А ой, это еще не раздел комментариев, тогда все же итог.

Итог не самый утешительный, как бы я не ругался на стандарты и «золотые правила» ими как пользовались, так и продолжат пользоваться. Да это хорошие, а в некоторых случаях идеальные инструменты для прикидок, после которых идет столько же оговорок как в IPC, но в реальности после идет «ой отвали, тут так написано, а те кто писали это люди не глупые, но я полность не читал, да и вообще у меня опыт 2 года в универе после пары в столовке за кульманом это делал пока смотрел на Галю». Но проблески есть, если я это все вам рассказал, а вы это всё прочитали, на пару‑тройку людей понимающих, что все гораздо зложнее станет больше

Спасибо! И не забутьте добавить карму если понравилось и проголосовать за статью

Литература

-

«Principles of Power Integrity for PDN Design» Larry D. Smith Eric Bogatin 2017

-

Брошюра «Целостность питания и ее влияние на целостность сигналов» Rohde & Schwarz

-

Презентация «EMC Control with PCB Design EMC Control with PCB Design for Working Engineers for Working Engineers» Dr. Bruce Archambeault IBM Distinguished Engineer and IEEE Fellow

-

Книга «High-Speed PCB Design Guide» Sierra Circuits Inc., 2020

-

https://resources.pcb.cadence.com/blog/2020-dc-voltage-management-in-your-pcb-its-all-about-the-pdn

-

Ott H. W. Electromagnetic Compatibility Engineering. Wiley, 2009.

-

Моделирование в программной среде ADS

-

AN 574: Printed Circuit Board (PCB) Power Delivery Network (PDN) Design Methodology

-

«Target Impedance Is Not Enough» Larry Smith, Steve Sandler, and Eric Bogatin January 16, 2019

-

Презентация «EMC Control with PCB Design EMC Control with PCB Design for Working Engineers for Working Engineers» Dr. Bruce Archambeault IBM Distinguished Engineer and IEEE Fellow

-

«PCB Design Guide to Via and Trace Currents and Temperature» Douglas Brooks and Dr. Johannes Adam 2021

-

Моделирование в программной среде ADS

-

Статья «Your Thermal Designs Are Inefficient» в журнале «Design007 Magazine, November 2023» от Douglas Brooks and Dr. Johannes Adam

-

https://resources.altium.com/ru/p/beyond-datasheet-real-world-testing-voltage-regulators

-

«Basics of Thermal Resistance and Heat Dissipation» ROHM Co., Ltd.

-

«How to Use the Thermal Resistance and Thermal Characteristics Parameters» ROHM Co., Ltd.

-

«Evaluation of Printed-Circuit Board Materials for High-Temperature Operation» Oriol Aviño-Salvado, Wissam Sabbah, Cyril Buttay, Herve Morel, and Pascal Bevilacqua

-

«High-Temperature Storage Testing of ACF Attached Sensor Structures» Sanna Lahokallio, Maija Hoikkanen, Jyrki Vuorinen and Laura Frisk

-

«Electrochemical migration behavior of moldy printed circuit boards in a 10 mT magnetic field» Xuan Liu, Ziheng Bai, Qianqian Liu, Yali Feng, Chaofang Dong, Lin Lu, Hong Luo, Jirui Wang, Shiwen Zouc and Kui Xiao

-

«Electromigration of power devices part 2: power device in applications in controlled environment» Hao Zhuang, Robert Bauer, Milad Mostofizadeh, Juliane Junesch Infineon Technologies AG

Автор: the_annnisss